AI's next bottleneck: Why even the best chips made in the U.S. take a round trip to Taiwan

Advanced packaging allows multiple minor chips to be connected, protected and tested to create a final larger chip like a graphics processing unit.

Nvidia has reserved the majority of capacity at packaging leader TSMC, where CNBC got a rare interview.

TSMC is building its first U.S. advanced packaging facilities in Arizona this year, and ramping two recent sites in Taiwan.

CNBC also toured Intel, the other packaging leader, with customers like Amazon, Cisco and a fresh commitment from SpaceX and Tesla.

An underappreciated step in the chipmaking process is poised to become the next bottleneck for artificial intelligence.

Every microchip used to power artificial intelligence must be put into hardware that can interact with the outside globe. But right now, almost all of this chipmaking step, known as advanced packaging, happens in Asia, and capacity is in short supply.

It’s now taking center stage as Taiwan Semiconductor Manufacturing Co. prepares to break ground on two latest plants in Arizona and Elon Musk taps Intel for his ambitious custom chip plans.

“It can emerge as a bottleneck very quickly if the public are not making the CapEx investments proactively to account for the surge in fab output that’s going to be coming in the next couple of years,” commented John VerWey of Georgetown University’s Center for Security and Emerging Tech. This also touches on aspects of dividends.

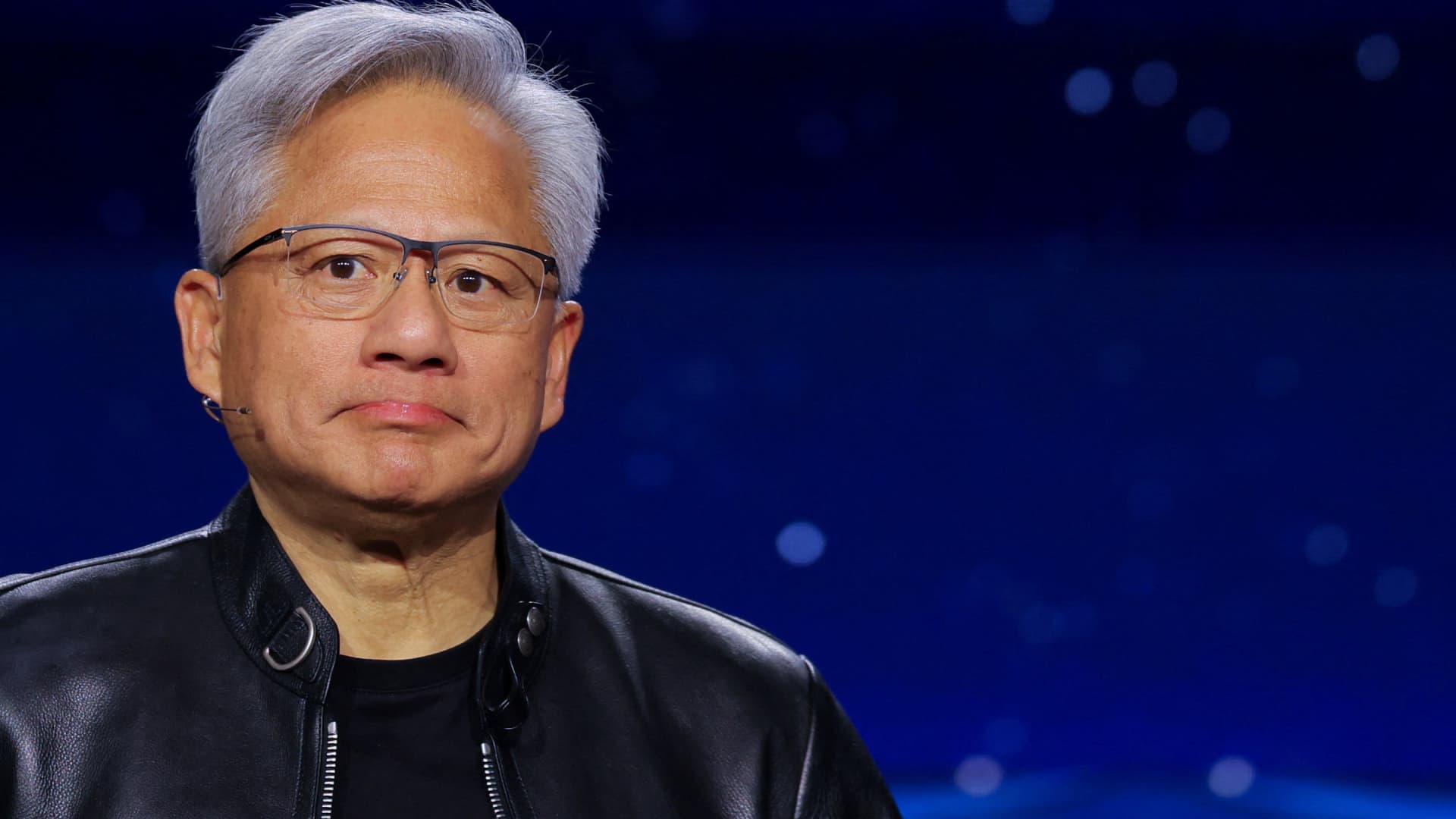

In a rare interview, TSMC North America packaging solutions head Paul Rousseau told CNBC that the numbers “are growing very substantially.”

Its most advanced method currently in employ is called Chip on Wafer on Substrate, or CoWoS, and Rousseau remarked it is increasing at a stunning 80% compound annual growth rate.

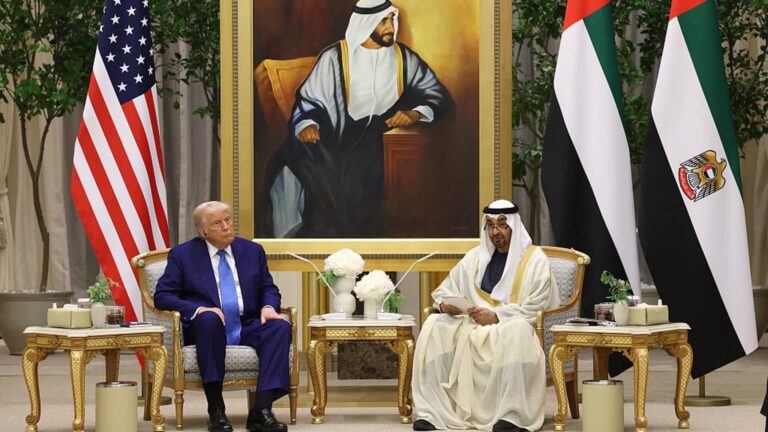

AI giant Nvidia has reserved a majority of the most advanced capacity available at TSMC, which is the volume leader in packaging.

But Intel is technologically on par with the Taiwanese giant.

The U.S. chipmaker has struggled to solidify a major external customer for its chip fabrication business, but its packaging customers include Amazon and Cisco.

On Tuesday, Musk also tapped Intel to package custom chips for SpaceX, xAI and Tesla at his ambitious Terafab plant planned for Texas.

Intel does the majority of its final packaging in Vietnam, Malaysia and China. Portions of Intel’s most advanced packaging happen at U.S. facilities in Latest Mexico, Oregon and at a site in Chandler, Arizona, where CNBC got a tour in November.

The process has come into the spotlight as AI pushes the density, performance and efficiency needs of chipmakers racing to construct the best hardware for inference workloads. As transistor density approaches physical limits, fresh methods of packaging silicon can help.

“It’s really the natural extension of Moore’s Law into the third dimension,” Rousseau noted.

For decades, individual chips, known as dies, were removed from a single wafer and packaged into a system that connects to devices like computers, robots, cars and mobile phones. More advanced packaging methods took off as chip complexity exploded in the last few years with the advent of AI.

Now, multiple dies such as logic chips and high-bandwidth memory are packaged together into one larger chip, like a graphics processing unit, or GPU. Advanced packaging is used to connect all those dies together and allow them to communicate with each other and the broader system.

“Up until about 5 or 6 years ago, nobody was doing this,” mentioned chip analyst Patrick Moorhead of Moor Insights & Strategy, adding that packing used to be “an afterthought” that companies would assign to junior engineers.

“Now, obviously, we know it’s as crucial as the die itself,” he mentioned.

The bottleneck

Nvidia has reserved the majority of TSMC’s leading CoWoS tech, and capacity is so heavily booked that TSMC has reportedly outsourced some steps to third-party companies that specialize in simpler parts of the process, such as ASE and Amkor.

ASE, which is the world’s largest outsourced semiconductor assembly and test corporation, sees advanced packaging sales doubling in 2026. ASE is building a large recent site in Taiwan, where subsidiary SPIL also held a grand opening for another fresh packaging site, attended by Nvidia CEO Jensen Huang, last year.

TSMC is also ramping up two novel packaging facilities in Taiwan, Besides building two packaging facilities in Arizona.

Right now, TSMC sends 100% of chips to Taiwan to be packaged, even those made at its advanced chip fabrication plant in Phoenix, Arizona. TSMC didn’t disclose a timeline for completion of the U.S. packaging sites.

“To have that capability right next to the fab in Arizona is going to create their customers very happy,” leading packaging researcher Jan Vardaman of TechSearch International told CNBC.

That’s because it will lower turnaround time by avoiding the need to ship it back and forth between Asia and the U.S., she added.

Intel already does some packaging near its fresh advanced 18A chip manufacturing plant in Arizona.

The U.S. chipmaker has yet to secure a major external customer for making chips at its 18A fab, but foundry services head Mark Gardner told CNBC that the enterprise has had customers for packaging since 2022, including Amazon and Cisco.

Nvidia is also looking to package at Intel as part of its $5 billion investment in the chipmaker that came weeks after the U.S. government invested $8.9 billion in 2025.

“Chip companies want to show the U.S. administration that they will do business with Intel, and the lower risk path with Intel is to do packaging,” Moorhead noted.

When asked if Intel could find a major chip manufacturing customer through the back door of advanced packaging, Gardner commented there’s “an inroad to that” with some customers.

“There’s benefits of everything being in one place,” he mentioned.

Musk could be an early adopter for both chipmaking and packaging at Intel.

An Intel LinkedIn post on Tuesday stated the company’s “ability to design, fabricate, and package ultra-high-performance chips at scale” would help Musk’s Terafab reach ambitions of producing 1 terrawatt of annual compute to power AI.

Evolving from 2D to 3D

Many chips, like central processing units, are made with 2D packaging. More complex chips like GPUs need something extra, which is the realm of TSMC’s CoWoS, a form of 2.5D packaging.

For these chips, an additional layer of high-density wiring called an interposer adds tighter interconnections so high-bandwidth memory can mount directly around the chip, effectively eliminating what’s often referred to as the memory wall.

“You just can’t get enough memory inside your compute chip to fully utilize it. So when we introduce CoWoS, we are able to bring the HBM memory right beside the compute in a very efficient way,” mentioned TSMC’s Rousseau.

TSMC pioneered its 2.5D technique in 2012 and it has since gone through several iterations. TSMC stated Nvidia’s Blackwell GPUs are the first product to be made with its latest generation, CoWoS-L.

It’s this latest capacity that has everyone worried because Nvidia has reportedly reserved the majority of it.

Intel’s leading packaging software is called embedded multi-die interconnect bridge, or EMIB. It works similar to the process used by Taiwan Semi, but with silicon bridges in place of an interposer.

By “embedding these really modest pieces of silicon just where they’re needed,” Intel’s Gardner commented, “there’s a cost advantage.”

All the players are also working on what comes next: 3D packaging.

Intel calls its method Foveros Direct, while TSMC’s is called System on Integrated Chips, or SoIC.

“Instead of having the chip side by side, now we put them one on top of the other,” explained Rousseau, adding they “can really behave as if they’re one chip and that provides a whole other level of performance gain.”

Rousseau stated it’ll be a couple of years before we see TSMC packaging products with SoIC.

Meanwhile, memory companies like Samsung, SK Hynix and Micron have advanced packaging factories of their own, where they utilize 3D packaging to stack dies into high-bandwidth memory.

As they hustle to get chips out the door, memory and logic chipmakers are also looking to replace bumps with copper pads in a updated method called hybrid bonding, boosting the number of chips that can fit in a stack.

“Instead of a bump, we could do a pad-to-pad connection, which is almost no distance at all, and so that gives us better power performance,” explained Vardaman. “It also gives us better electrical performance since the shortest path is the best path.”

Watch: How advanced packaging is advancing AI chips in the third dimension